ICパッケージ技術入門

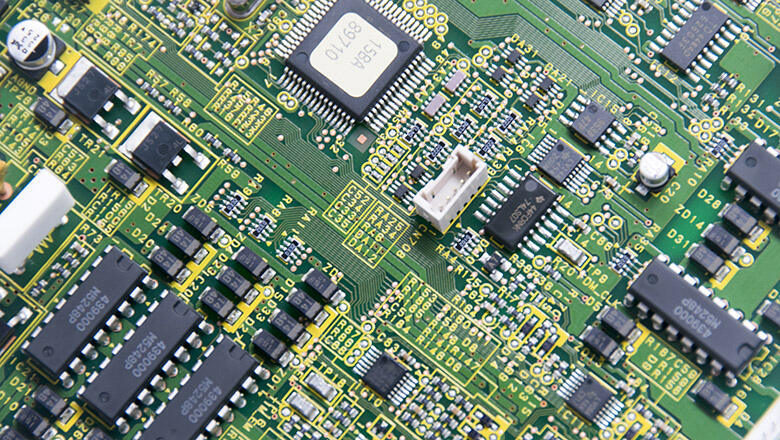

集積回路(IC)は、すべての現代電子システムの基盤を成している。そのパッケージ技術は、シリコンチップと外部環境との間の重要なインターフェースを提供し、大規模な応用、小型化、高信頼性動作を可能にする。本ガイドでは、初期の画期的な進展から現在の最先端ソリューションまで、集積回路パッケージ技術の発展の歴史を追う。

優れたチップパッケージは、チップを保護するだけでなく、安定した電気的性能、効率的な放熱、簡便な製造プロセス、高い耐久性といった要件を満たさなければならない。従来のDIPパッケージから、3DパッケージやFOWLPといった革新的技術に至るまで、パッケージ技術は絶えず進化している。

ICパッケージの基礎

ICパッケージとは何か? なぜ重要なのか?

集積回路(IC)パッケージは、電子システム内でチップ(またはマルチチップモジュールおよび先進パッケージの場合)を安全に実装および相互接続するための保護外装です。その主な機能には以下のものが含まれます:

- 保護: 集積回路チップを湿気、衝撃、汚染、静電気放電から保護する。

- 電気接続: 金属ワイヤ、はんだボール、またはパッドを通じてチップがより大きなシステムに接続され、強力な信号伝送が可能になる。

- 熱管理 集積回路によって発生する熱をプリント基板や周囲環境へと効果的に放散し、信頼性の高い連続的な動作を確保する。放熱性能の向上は、高電力・高周波回路において極めて重要である。

- 識別: この文書には、組立、運転、保守に必要なすべての情報に加え、法的および規制要件への適合に関する情報が含まれている。

本包括ガイドの範囲

ICパッケージの選定と設計に関するこのガイドは、次の質問に答えます:

- 一般的なICパッケージの種類にはどのようなものがあるか?

- 電子工学、熱力学、機械工学および製造の観点から、さまざまなICパッケージ間で共通する点と異なる点は何でしょうか?

- 半導体技術の進化に伴い、ICパッケージ技術はどのように変化してきたのでしょうか?

- AI、5G、およびモノのインターネット(IoT)において、革新的な新しいパッケージ技術はどの程度重要なのでしょうか?

- どのパッケージソリューションがあなたのアプリケーション要件に最も適しているでしょうか?

要するに、これは包括的かつ重要なガイドです。このガイドは、集積回路の種類を理解し、適切なパッケージを選択し、パッケージ技術における世界的な動向を把握するうえで読者を支援することを目的としています。

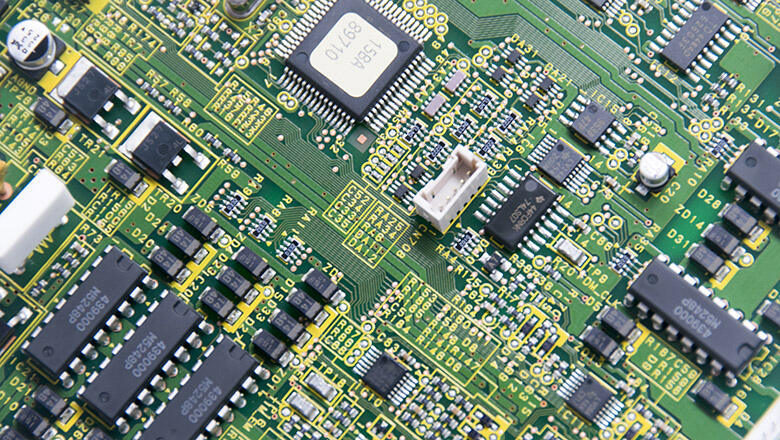

ICパッケージの構成要素

基本的なパッケージ構成部品

パッケージの種類に関わらず、すべての集積回路パッケージはいくつかの基本的な構成部品を共有しており、これらを組み合わせることで高性能で信頼性の高い電子製品が実現します。

- ICダイ(チップ): ダイは通常、シリコンを主材料として、高度な半導体製造技術を用いて作られます。

- パッケージ基板: チップをワイヤボンディングまたはフリップチップ技術で確実に接続でき、チップと外部のリードやはんだボール間での信号伝送のためのプラットフォームを提供します。

- リード、ボール、またはパッド: これらの端子はパッケージの側面、底面、またはすべての周囲に配置され、プリント基板(PCB)への接続に使用されます。

- 封止材または密封材: 機械的および環境保護のために使用されるプラスチックまたはセラミック材料。

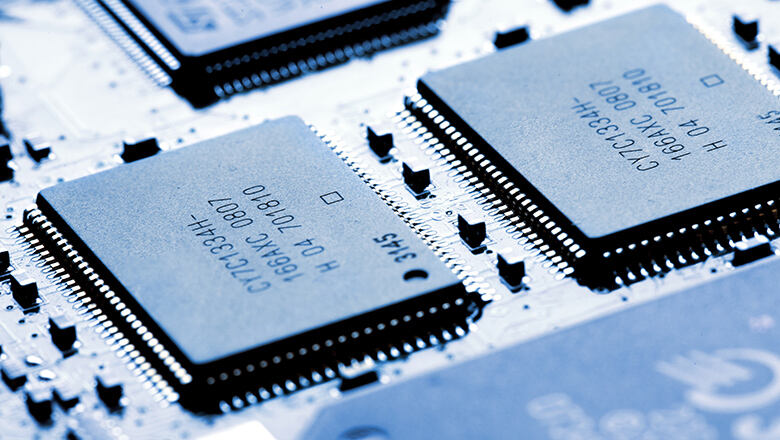

- 刻印: 識別マーク、ロット番号、方向マーク、および偽造防止機能が含まれる場合があります。

- 熱性能向上機能: 露出したサーマルパッド、ヒートシンク、ヒートプレートにより、熱管理を向上させることができます。

ICパッケージ材料および機械的特性

ICパッケージング用材料

パッケージング技術がますます複雑化するにつれて、パッケージング材料の選定はますます重要になっています。

- プラスチック/エポキシ: 費用が比較的安価で、ほとんどの商業用途に適していますが、高温・高湿環境下での性能には制限があります。

- セラミック: 優れた信頼性を備えており、高電力用途や軍事・航空宇宙用途に適しており、特に高い熱的および機械的ストレスに耐えることができます。

- 金属/複合材料: ヒートシンクやリードフレームは、パワー半導体や高周波応用分野で increasingly 使用されています。

パッケージング材料一覧表:

パッケージの種類 |

代表的な素材 |

ケース |

主なメリット |

プラスチック/エポキシ |

エポキシ樹脂、プラスチック |

消費者向け、SMD、DIP |

コスト、大量生産が容易 |

セラミック |

Al2O3、SiNなど |

軍事、自動車、電力 |

高度な熱管理、信頼性 |

複合材料、金属ベース |

銅合金、合金 |

電力、高周波 |

放熱、性能 |

機械的特性およびパッケージ機能

- 振動・衝撃耐性: 自動車、航空宇宙、産業用エレクトロニクス業界にとって極めて重要です。

- 湿気に弱い: 湿気感受性レベル(MSL)に基づき、プラスチック包装は慎重な保管・取り扱いが必要です。

- パッケージ寸法: これはPCBのレイアウト、3D ICアプリケーションにおける積層高さ、およびモバイルデバイスの厚みに影響を与えます。

- 表面実装対応性: 部品を直接PCBに接続することで、このパッケージ方式はより効率的な自動組立を可能にします。

ICパッケージの種類、サイズ、および分類

IoT、高性能コンピューティング、自動車、ウェアラブルデバイスなどの分野におけるアプリケーションの爆発的成長を支えるために、さまざまなパッケージタイプが登場しています。

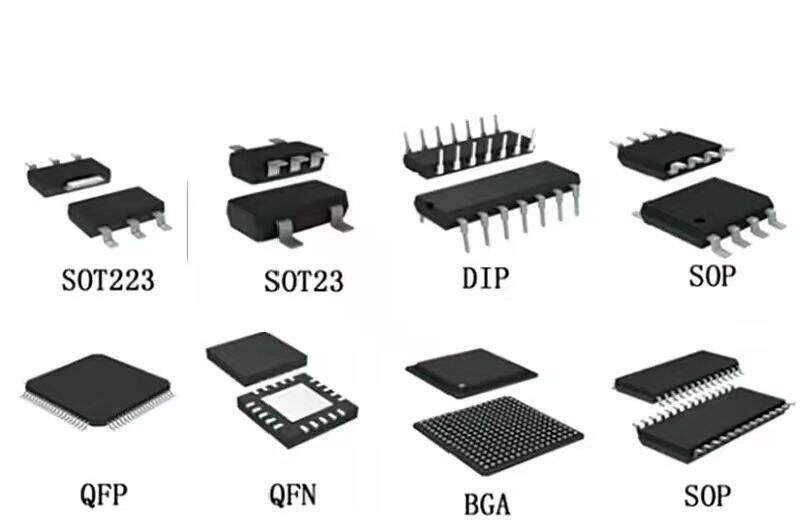

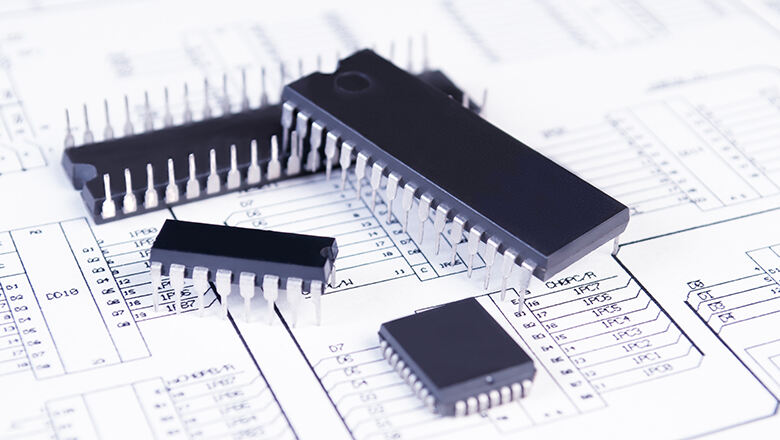

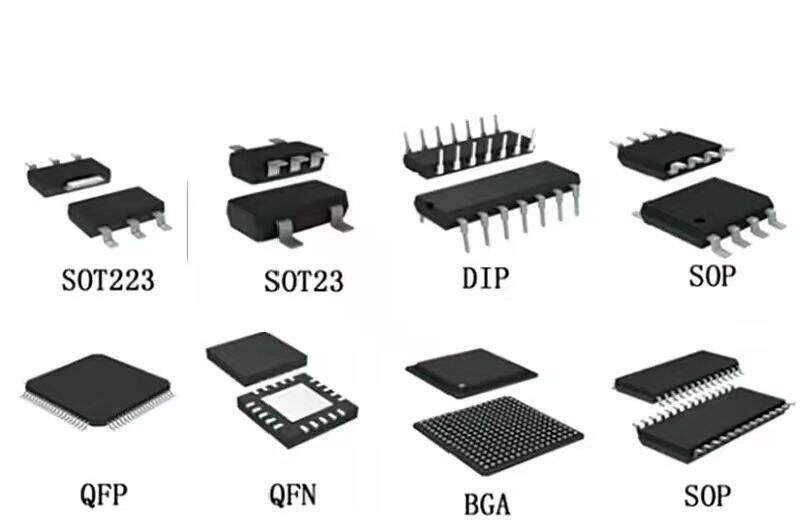

スルーホール技術

- デュアルインラインパッケージ (DIP): 最も初期の集積回路パッケージです。これらの部品は小型で信頼性が高く、接続や交換が容易です。現在でもプロトタイプ、電源システム、および古い製品に使用されています。

- TO-92、TO-220: このタイプのパッケージは、小信号用トランジスタ(TO-92)および電力機器(TO-220)によく使用され、確実な取り付けとヒートシンクへの簡単な接続が可能です。

表面実装技術 ( SMT ) および表面実装パッケージ

- スモールアウトラインパッケージ (SOP)、SOIC: 表面実装型のSOPパッケージは、民生用電子機器や自動車用電子機器で広く使用されています。SOPパッケージはSOICパッケージよりも薄型であるため、PCB上の配線密度を高めることができます。

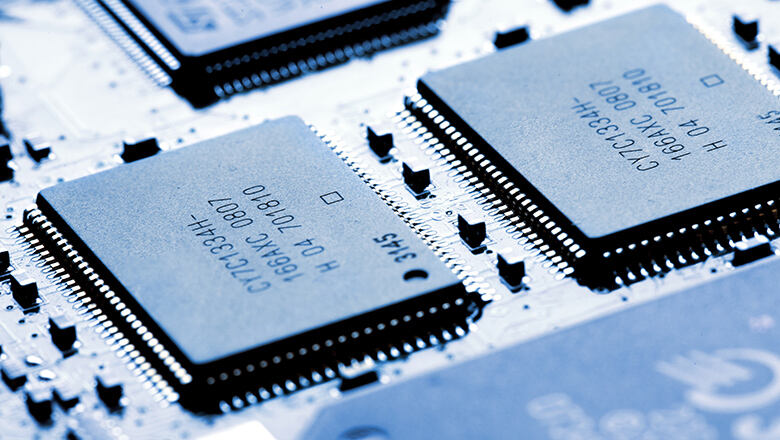

- 四方向フラットパッケージ (QFP): このパッケージは4辺すべてにピンがあり、多数のピンを持つマイクロコントローラーやフィールドプログラマブルゲートアレイ(FPGA)に適しています。

- クワッド・フラット・ノーリード (QFN): ピンはパッケージ本体を超えて延びておらず、パッドはパッケージの底部に配置されています。この設計の主な利点は、放熱性に優れ、スペースを効率的に利用できる点です。

- スモール・アウトライン・トランジスタ (SOT): 表面実装技術で使用される小型のトランジスタ/ダイオードは、高密度です。

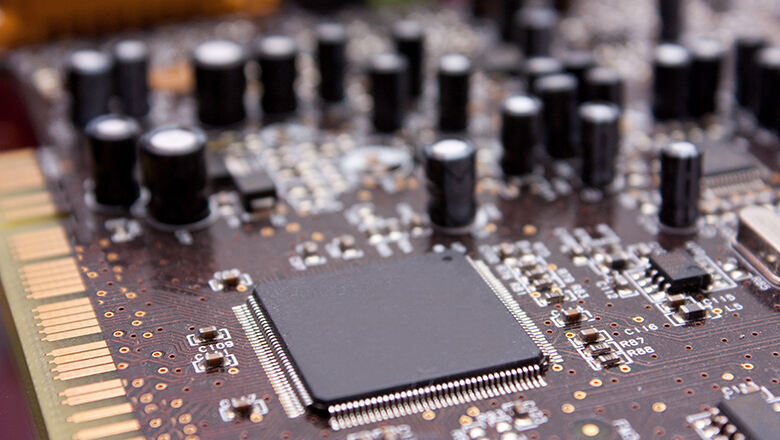

アレイおよび高度なICパッケージ技術

- ボールグリッドアレイ (BGA): チップ下面にあるはんだボールはグリッド状に配置されています。この設計は、数百から数千もの接続密度を持つため、CPU、FPGA、高速メモリに最適です。

- ランドグリッドアレイ (LGA): BGAと類似していますが、金メッキされたパッドを備えており、サーバー用CPUに理想的で、高い信頼性と高密度を提供します。

- チップスケールパッケージ (CSP): チップ自体とほぼ同じサイズ—スマートフォン、医療機器、IoT(モノのインターネット)に最適です。

- ウェハーレベルパッケージング (WLP): これらのパッケージはウェハー段階で直接形成され、超小型で高性能、低背のソリューションを実現します。

特殊高度パッケージ(続き)

- システムインパッケージ (SiP): 複数のチップおよび受動/能動部品が単一のパッケージに統合されています。これらのチップはウェアラブルデバイス、マイクロラジオ、高度なIC、およびIoTノードに適しています。スペースの使用効率を最大化し、複数の機能を一つのパッケージに集約します。

- 3D IC/3D ICパッケージング/3Dパッケージング: スタッキングされたチップ構造(シリコン貫通ビアおよびウェハー接合技術を利用)により、高帯域幅のチップ間通信と比類ない集積度を実現します。3D ICは最先端のAIプロセッサーやハイエンドモバイルSoCの特徴です。

ICパッケージの種類と用途

ICパッケージタイプ |

組み立てプロセス |

代表的なアプリケーション |

パッケージの特徴 |

DIP(スルーホール) |

はんだ付け、ソケット実装 |

レガシー、プロトタイピング、アナログ用途 |

大型で取り扱いが容易 |

SOIC/SOP(SMD) |

地上設置型 |

民生用、自動車用 |

コンパクトでコスト効果に優れた |

QFP/QFN(SMD) |

地上設置型 |

MCU、FPGA、ワイヤレス、SMC |

ピン数が多く高密度 |

バイアス |

表面実装(リフロー) |

CPU、GPU、メモリ |

高I/O、熱性能の向上 |

CSP/WLP |

ウェハーレベル、SMD |

モバイル、センサー、IoT |

超小型、低背型 |

SiP/3D IC |

カスタム/高度なプロセス |

ウェアラブル、サーバー、高性能AI |

マルチダイ、高度なパフォーマンス |

ICパッケージに記載された情報

各集積回路パッケージにレーザーでマーキングまたは彫刻された情報は、アセンブリだけでなくシステム性能にも影響するため非常に重要です。

- 品番およびパッケージタイプ: 識別、調達、品質管理のため。

- パッケージ寸法/外形: 設計およびパッド配置におけるサイズ、リードピッチ、および配置を規定します。

- ピン構成: ピン、パッド、またはボールの配列と、それらが表す信号または機能。

- 材料/環境に関する詳細: RoHS指令に準拠し、鉛フリーで、湿気や化学物質に対する保護機能を備えています。

- ロットコードおよび日付コード: 品質および保証追跡のためのトレーサビリティ。

- 向きおよび組立マーク: ノッチ、ドット、面取り、またはレーザーマークは、ピン1および正しい向きを示します。

- 熱定格: 最大接合部温度、消費電力、および熱性能向上のためのガイドライン。

パッケージ設計は厳格な規格に基づいており、信頼性、相互運用性および製造適正を保証します。

- IPC-7351: 表面実装デバイスパッケージ用の標準パッドパターンを定義し、PCB設計および自動実装におけるパッケージの一貫性を確保します。

- ANSI Y32.2-1975: すべてのタイプのICパッケージに使用される回路図記号を定義しています。

- ISO 10303-21: STEP形式は、設計ツール間でパッケージ外形および寸法の3Dモデルを交換する上で不可欠です。

- JEDECおよびSEMI標準化: 特にマルチソース半導体パッケージにおいて、熱定格、湿気感度、テスト容易性、パッケージ互換性が非常に重要です。

- RoHS/REACH適合: 集積回路のパッケージ材料が、世界的な環境基準を満たしていることを確認します。

ICパッケージ設計の規則とベストプラクティス

集積回路のパッケージ設計では、電気的、熱的、機械的な要件を幅広く考慮する必要があります。これには以下の項目が含まれます:

- IPCおよびJEDECのフットプリントガイドラインに従ってください。 表面実装パッケージ向けに最適化されたパッドパターン。

- サーマルパスを最適化してください。 エクスポーズドパッド、サーマルビア、および熱パッケージ直下の十分な銅層を使用してください。

- パッドおよびピンピッチを確認してください。 実装プロセスの精度に合ったパッケージピッチを選択してください。細ピッチのBGAやQFNはX線検査を必要とする場合があり、実装コストが増加する可能性があります。

- 明確な向きマークを利用してください。 パッケージ上のピン1は明確にマークされ、PCBのシルクスクリーンと一致させて配置し、実装エラーを防止します。

- 製造を念頭に置いた設計: 同一PCB上であまりにも多くのパッケージタイプを使用しないこと。可能な限り標準的で量産されているパッケージを選択し、最適なパッケージコストとサプライチェーンの安定性を確保してください。

- シミュレーションツールを活用してください。 最新の電子設計自動化(EDA)キットは、信号の完全性、機械的応力、および熱性能をシミュレーションでき、高度なパッケージ選定と統合をより信頼性の高いものにします。

適切なICパッケージの選び方

パッケージまたはパッケージタイプを選択する際に、以下の要素を検討してください:

- 性能要件: 高速、低ノイズ、または高電力密度の用途では、BGAまたは3D ICパッケージがより適しています。SOICまたはQFNパッケージは、多くの中電力用途に対して費用対効果の高いソリューションを提供します。

- 熱的要因: CPUや電源用ICはより優れた放熱が必要です。ヒートシンク、サーマルパッド、または先進的な基板技術を備えたパッケージを検討してください。

- 機械的および環境的要件: 振動、衝撃、湿気などの要因を考慮する必要がある場合(例えば、自動車や産業制御アプリケーションなど)、高度なセラミックまたは金属製パッケージは最大限の保護を提供できます。

- 製造性および実装: SMTパッケージは自動組立において最も高いスループットを提供します。一方、プロトタイピングや高信頼性が要求される特定の用途にはスルーホールパッケージが適している場合があります。

- パッケージサイズとPCBの制約: 極めてコンパクトなフォームファクタ(ポータブルデバイス、補聴器など)にはCSP、QFN、WLPを使用してください。ブレッドボード対応または従来型の製品にはDIPまたはSOICを使用してください。

- コストとサプライチェーン: 標準的なパッケージソリューションは通常、パッケージコストを削減し、納期を短縮できます。量産向けの設計では、一般的で既製のパッケージタイプを選択することに注力しています。これにより部品の調達が容易になり、コストを抑えることができます。

ICパッケージングにおける課題と制限

半導体パッケージ技術は大きく進歩しましたが、依然として注目が必要な継続的な課題があります:

- 熱放出: チップの消費電力が増加し続けるにつれて、従来のパッケージの信頼性のある放熱能力は限界に近づいています。FOWLPや内蔵熱経路といった新しい技術開発がある中でも、特に発熱量の大きいSoCではパッケージの選定が依然として非常に重要です。

- 小型化の限界: パッケージサイズが小さくなるにつれ、微細構造の実装、変形、検査の難易度が上昇します(特にBGAおよびWLPにおいて)。これにより、現場での高価な故障リスクが増大します。

- 高周波における信号完全性: より高いデータ伝送速度は、パッケージ内部での信号損失、クロストーク、電磁干渉の制御がより困難になることを意味します。先進的な基板およびシールド設計は性能を向上させますが、同時にパッケージコストも上昇させます。

- 機械的信頼性: パッケージは、衝撃、振動、繰り返しの温度変化に耐えられる必要があります。特に自動車や産業用電子機器のように過酷な環境下での使用において重要です。

- 環境および規制コンプライアンス: ますます厳格化する規制に対応するため、製造業者は包装材が無毒で、リサイクル可能であり、グローバルなRoHS/REACH/環境基準に適合していることを確実にする必要があります。

- 複雑な組立工程: 高度なパッケージングプロセス(SiP、3D IC、FOWLP)では、チップの積層、ウェハーレベルでの製造、複雑なワイヤボンディングまたはフリップチップ技術などが組立工程に含まれます。

ICパッケージ技術の将来の動向

近未来のパッケージング革新

- ファンアウト・ウェハーレベルパッケージング(FOWLP): 高度な回路パッケージ統合プロセスでは、チップをサブストレート上に配置し、封止した後、微細配線によって再配線を行うことで、薄型かつ拡張性のある形態で高いI/O性能と放熱性能を実現します。

- 3Dパッケージングおよびチップレット: 真の3D ICスタッキング、チップベースのシステム統合、および垂直/水平インターコネクトを備えた先進的なパッケージング技術により、単一パッケージ内での次世代の性能スケーラビリティと機能性が定義されています。

- 生物分解性のある材料: 電子廃棄物を最小限に抑えるため、堆肥化可能なプラスチックや無毒の封止材など、集積回路用の包装材料の研究が進められており、すでに一部の使い捨て消費者向け製品で使用されています。

- スマートパッケージ: 健康センサ、アクティブ冷却(マイクロ流体/ペルティエ効果)、圧力および温度の自己監視機能を組み合わせることは、重要な用途において有利です。

- AI駆動型パッケージ設計: AIは現在、パッケージタイプ、ピン割り当て、基板構造の自動最適化を加速することができ、電気的、熱的、コスト面の性能を同時に向上させます。

ICパッケージ技術に関するよくある質問(FAQ)

Q: 現在最も一般的なICパッケージの種類は何ですか?

A: SOP、QFP、QFN、BGA、CSP、WLPは、現代の電子製品で一般的なパッケージタイプとなっています。ただし、実装用穴あきパッケージ(DIP、TO-220)は、依然として特定の特殊用途やプロトタイプ製品で使用されています。

Q: サーフェスマウントパッケージとスルーホール技術の違いは何ですか?

A: サーフェスマウントデバイスは、プリント基板の表面に直接自動組み立てできるように設計されており、小型のパッケージサイズ、高密度の回路構成、およびより信頼性の高い高速動作が特徴です。一方、スルーホール実装技術では、部品のリードをPCB上の事前に開けられた穴に挿入する必要があり、堅牢な機械的接続が可能ですが、より多くの基板面積を必要とします。現代の大規模生産においてサーフェスマウント技術が業界標準となっている一方で、スルーホール技術は依然としてプロトタイプ検証、パワーエレクトロニクス、および高い機械的強度が求められる用途において不可欠です。

Q: 先進的なICで現在使用されている革新的なパッケージング技術は何ですか?

A: 先進的な集積回路(IC)パッケージング技術には、3D ICパッケージング、ファンアウトウエハーレベルパッケージング、システムインパッケージング、チップレベルパッケージング、および現代的なワイヤボンディングやフリップチップボンディング技術が含まれます。これらの手法により、電気的性能を効果的に向上させ、高ピン密度を実現し、放熱効率を大幅に最適化できます。これは高出力または高周波の集積回路アプリケーションにとって極めて重要です。

Q: 高速回路およびAIのニーズに対応するために、ICパッケージングはどのように進化してきましたか?

A: データセンター、AIアクセラレータ、5Gの登場に伴い、集積回路のパッケージング技術は、寄生効果を最小限に抑え、熱性能を向上させるために継続的に進化しなければなりません。BGA、先進基板、熱伝導性ビア、3Dパッケージング、埋め込み型受動部品などのパッケージングソリューションは不可欠となっています。3D集積回路およびチップアーキテクチャにより、複数の機能的コンポーネントを単一のパッケージに高密度で統合することが可能となり、計算密度とエネルギー効率を大幅に向上させます。

Q: 高信頼性または過酷な環境に最適なパッケージング材料はどれですか?

A: セラミックおよび金属パッケージは、優れた機械的強度、熱伝導性、環境耐性を備えており、自動車、軍事、航空宇宙産業の用途に最適な選択肢となります。民生用電子機器や汎用電子製品では、良好な密封性を持つプラスチックおよび複合材パッケージが、コストパフォーマンスと耐久性の面で最も適切なバランスを実現します。

Q: アプリケーションに適したパッケージを選ぶにはどうすればよいですか?

A: 集積回路パッケージの種類を選定する際には、電気的特性、消費電力、パッケージサイズの制限、利用可能な製造プロセス、エンドユーザーの信頼性要件を考慮する必要があります。同様に重要なのは、サプライチェーンの安定性、所有総コスト(組立および検査を含む)、関連する認証(RoHS、JEDEC、IPC適合)です。この集積回路パッケージ選定の包括的なガイドは、段階的なアドバイスを提供します!

まとめ

電子機器における小型化、高速化、高エネルギー効率、高信頼性への需要が高まるにつれて、集積回路のパッケージング技術は前例のない発展を遂げています。現代のパッケージング技術は、精密なシリコンチップと堅牢な相互接続デバイスを結ぶ重要な橋渡しとして、スマートウェアラブルデバイスから自律走行車両に至るまで、さまざまな分野での革新的な応用を支えています。この集積回路パッケージング技術の包括的なガイドでご確認いただけるように、適切なパッケージングソリューションの選定は二次的な考慮事項ではなく、あらゆる集積回路や電子部品の成功・失敗を決める核心的な鍵です。